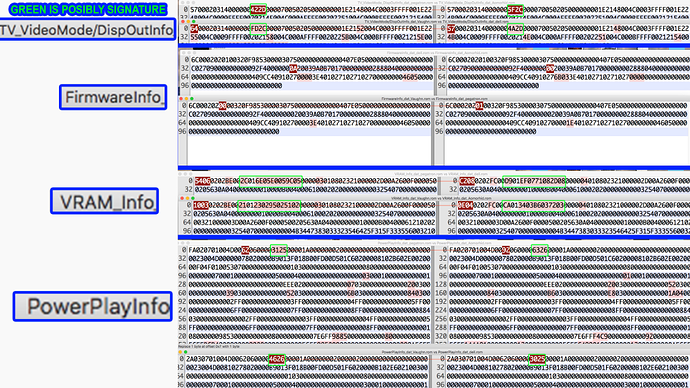

Hi! I’m working on app for rebuilding modules in vbios. And early method working fine. But I stuck with vbios signature verification. I compare all modules of four vbioses and find out that PowerPlayInfo includes some different two bytes 3125, 3025, 4626, 6326… etc… so possibly they are signatures.

[/img]Then i tried to understand Vbios header, and that is what i made:

55 AA FILE MASK