@Vlad00n memory timings are subjective depending on if you are aiming for highest possible frequency with lowest possible timings or simply running stock frequency with tight timings. If you want the latter start with a TRRD of 5 or 6 and IMC between 0.9v - 0.96v. If you want the latter start with a TRRD of 7 (8 is only really needed when pushing for 2300MHz+ but efficiency starts taking a hit at this point). Any 580/590 card I tested I generally settled on 2200MHz as that was always the optimal speed to efficiency barrier but not all memory is going to be able to hit 2200MHz it’s a pretty hard slog getting a card stable at that speed, 2150MHz is much easier and if you are looking for maximum speed at lowest possible voltage for power efficiency then definitely aim for 2150MHz as the IMC should be perfectly happy running that speed on 0.85v-0.9v.

@ket I’m not aiming for higher clocks, 2150-2175 is the max that I want. At this point I have 1411 Mhz Core with 1085mv, and memory with the strap that I thanked you about with 2150 and 960mv on the Mem controller. Don’t want to push more voltages to the memory, neither to the core, these settings are good for me. I would like to keep the card cool and efficient as you said. If you have any suggestions for a bit better timings, I would happily test them. And this will be my final tuning of this card ![]()

Hello @ket.

For 1 month now I’m using this strap : 777000000000000022EE9C00106A7D4DA06914153C8EC60B004684007D0714204A8900A00200712414143F48BC324C1A with 945mv on the IMC, 2150Mhz mem clock, and core clock of 1411MHz at 1085mv. With these settings I got only 1 memory error once, so I decided that I could live with that. But today I got a lot of artefacting.

I red your comment about the ras timings that they could still be relaxed, but probably my memory could not handle that. Could you please give me and advice what can I change to fix the issue.

####SEQ_WR_CTL_D1####

DAT_DLY = 7

DQS_DLY = 7

DQS_XTR = 0

DAT_2Y_DLY = 0

ADR_2Y_DLY = 0

CMD_2Y_DLY = 0

OEN_DLY = 7

OEN_EXT = 0

OEN_SEL = 0

ODT_DLY = 0

ODT_EXT = 0

ADR_DLY = 0

CMD_DLY = 0

####SEQ_WR_CTL_2####

DAT_DLY_H_D0 = 0

DQS_DLY_H_D0 = 0

OEN_DLY_H_D0 = 0

DAT_DLY_H_D1 = 0

DQS_DLY_H_D1 = 0

OEN_DLY_H_D1 = 0

WCDR_EN = 0

####SEQ_PMG_TIMING####

TCKSRE = 2

TCKSRX = 2

TCKE_PULSE = 14

TCKE = 14

SEQ_IDLE = 7

TCKE_PULSE_MSB = 1

SEQ_IDLE_SS = 0

####SEQ_RAS_TIMING####

TRCDW = 16=>?

TRCDWA = 16=>?

TRCDR = 26=>?

TRCDRA = 26=>?

TRRD = 7

TRC = 77

####SEQ_CAS_TIMING####

TNOPW = 0

TNOPR = 0

TR2W = 26=>27

TCCDL = 4

TCCDS = 6

TW2R = 20

TCL = 21

####SEQ_MISC_TIMING####

TRP_WRA = 60

TRP_RDA = 28

TRP = 26

TRFC = 188

####SEQ_MISC_TIMING2####

PA2RDATA = 0

PA2WDATA = 0

TFAW = 6=>7

TCRCRL = 2

TCRCWL = 4

T32AW = 4

TWDATATR = 0

####ARB_DRAM_TIMING####

ACTRD = 20=>22

ACTWR = 20=>22

RASMACTRD = 63

RASMACTWR = 72

####ARB_DRAM_TIMING2####

RAS2RAS = 188

RP = 50

WRPLUSRP = 76

BUS_TURN = 26

####MC_SEQ_MISC####

MC_SEQ_MISC1 = 0x2014077D

MC_SEQ_MISC3 = 0xA000894A

MC_SEQ_MISC8 = 0x24710002

Please tell me your opinion.

Thank you in advance.

TR2W 28, TRP_WRA 62, TRP_RDA 29, TFAW 4, RP 56. Once you verify that’s stable you can try stepping down TRP_RDA to 28.

There you said something! I got one almost two years ago for my ten years old office PC, and I chose it because it available and affordable (mining boom was just cooling down). I had to cut out the hard drive cage from the PC case to make it fit. Since then I spent dozens (hundreds?) of hours in fan curves, voltage an fequency settings and bios mods. As I could not get it fast, cool AND silent, I made custom front and backplates to apply a CPU tower cooler with two 140mm fans (shhhh…!).

I had more fun in modding the card than in using it for games.

Now I’m almost satisfied, but I struggle with that damn memory settings.

The memory runs rock stable at 2250MHz/1000mV with 1750MHz timing strap and tREF = 5000.

It also runs up to 2400MHz/1000mV for a certain time, but not stable, as it produces thousands of memory errors and it did run on 1500Mhz timing strap for some time, but now crashes every time I try to load them.

With the stable settings I get about 250GByte/s and my question is - what can I expect from Hynix memory? Is it worth trying to optimize some more? I haven’t succeeded so far…

Best regards,

Hauke

Nothing more, I’d say after two days of trying.

The only thing is, how do I get tREF into the strap? I can’t find it in your listing, @ket

if some of you here have as much of an interest in gaining control over any and all performance-related configuration (gpu bios, mobo bios) as you seem to have then contact me.

this got me

RX560 is also excluded from BIOS signature check in driver

for example

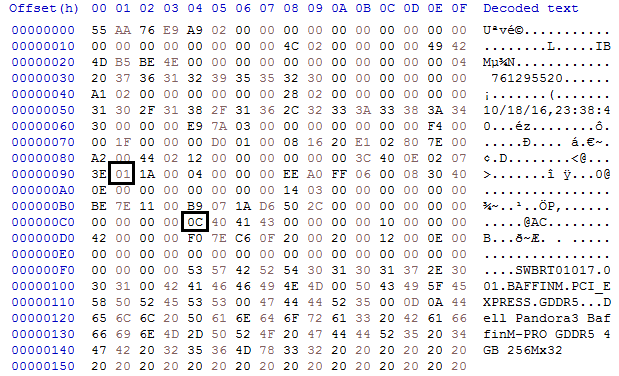

F0 7E C6 0F are IDs of RX460 card

revison consists of major and minor ver ID, not sure which one is which, the one 0F seems to be always forced with value from chip, but the other one can be changed in BIOS

F0 7F E6 0F will give 67FF rev EF and that one matches RX560 in driver inf file

by the way, the opengl improvements are actually working here as well on the mobile system it just damn furmark that doesn’t show any difference, testing with two other benchmark tools scores are about twice of those with 21.3.1 driver which also sucks compared to a year older 20.4 driver

in general, comparing 20.4 with 23.4.1 there is about 50% better performance with opengl

for anyone looking how to enable tuning in adrenalin with laptop polaris it is simple

there are max core and max mem clock as well as power limit fields in powerplay table, on laptop systems these are all zeroed out.

it is enough to enter sane values into vBIOS here, flash it and reinstall adrenalin drivers

tuning section appears in utility so you can get rid of msi afterburner’s hacky method

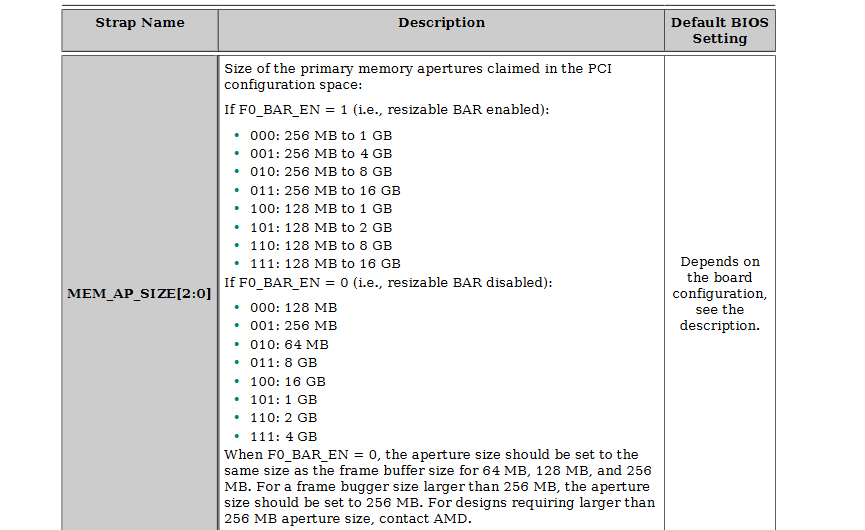

resizable BAR and it’s size can be changed on polaris. this might be interesting to @Kuri0 and guys that have problems with specific BAR size

in the location 0x91 you disable/enable resizable BAR while in 0xC4 you set the max supported size (bits 5:3)

if the resizable BAR is disabled the values from 0xC4 are used for fixed BAR size

How to change the max supported BAR size on polaris vbios? Does it requires magic gop and ati vbios patcher?

you enter values to the 3-5 bits of 0xC4 according to

whatever you need to do when you do any other BIOS mod. so crc patch that PBE does, about gop i don’t know it is not used on this system with polaris

Im a bit confused, mine explaining it?

look in first screenshot, it is 0C in the 0xC4 offset, so type C in calculator (hex mode) and switch mode to bin you get 1100. always start from right and from 0 count to left.

so with 0C bit0 and bit1 are 0, bit2 and bit3 are 1, other bits not displayed in calculator (a simple one that come with windows) meaning they are zero so from example i have 001 which is 256MB to 4GB, or 256MB if reBAR disabled

when you decide the value type it in bin mode to calculator and switch to hex mode to get value you enter in vbios. bits 0, 1 and 2 you don’t change i think they can soft brick the GPU, don’t remember precisely

Hello mate! Lots of great info in here…im just getting into extreme oc…and my first victim is an rx580 sapphire nitro+ special edition…im just going for max oc voltages etc…i have the core up to 1615mh…1.375v…i have gone up to 1.5v but doesnt want to play…it seems my memory may be the issue…timings etc…any chance you could have a look at the bios please?

@Grindcore77 As I’ve said before Polaris isn’t frequency starved. Doesn’t matter if the GPU is running 1.4GHz~ or 1.6GHz+ with massive volts you’re going to see little to no benefit, certainly no benefit warranting the copious heat and power draw. Memory timings and bandwidth are king. I tested a few different RX580s and 590s the latter performed identical despite a 100MHz or more core frequency advantage with the cards running identical memory frequency (8.8GHz) and timings. There’s only so much you can obtain from an architecture before the technology itself becomes the limiting factor. With AMD apparently starting to sell the 2048SP version of the RX580 again (aka RX4\570) we might see that die shrunk RX590 I’ve always talked about with GDDR6 memory.

Understood…will have to look into it more…any advantage however small despite power and heat is a non issue…only going for benchmark scores…if its extra volts for a few mhz all for a few points,its happening! Haha

The card im learning on is using samsung memory…so will go through this guide again and see how i go…

@Grindcore77 Honestly beyond 1.5GHz core speed the differences are within margin of error even in benchmarks you’re wasting your time you’d be better spent sitting with the lower voltages and heat\power draw output so the card can maintain maximum GPU frequency more often (if not constantly) while at the same time the memory staying cooler so it should be able to be pushed further but take it from someone that absolutely knows what they are talking about here; getting to 9GHz memory frequency 100% stable isn’t easy and it’s harder still optimising the timings at that frequency for better performance than you can get at 8.4-8.8GHz. As you’re working with Samsung memory you’re already handicapped no card I ever had could get anywhere near those frequencies regardless of what I did I hit 9GHz with a card that had Micron memory, Hynix cards reliably did 8.6-8.8GHz, one did 9GHz with a lot of coaxing.

Ok i hear you…so all these top graphics scores in 3dmark with insane clocks…1900,1800,1700…they would be top scorers without those clocks and better memory timings?