hmm edited/deleted my prev post by accident.

yes, I am stuck at the same spot. Asus Z87 boards are SOL

@MeatWar

Okay I will try again when it isn’t 2:25AM local time! ![]()

![]()

![]()

This is just the text string for setting that was not added at all.

An SDl token controls If it the setting will be added in the build proces or not.

PciBus

TOKEN

Name = "ABOVE_4G_PCI_DECODE"

Value = "0" Off

Help = "Tells if Chipset supports decoding of PCI\resources in Above 4G Address Space. Sets EFI_PCI_HOST_BRIDGE_MEM64_DECODE in Allocation Attributes."

TokenType = Boolean

TargetH = Yes

Range = "ON or OFF"

If the token is not set, the setting is not being defined in Setup and more likely in NVRAM too.

PciPort

if ABOVE_4G_PCI_DECODE

PciSetupData->Above4gDecode = SetupData->Above4gDecode;

endif

PciBus

#ifdef SETUP_DATA_DEFINITION

/***********************************************************/

/* Put NVRAM data definitions here.

/* For example: UINT8 Data1;

/* These definitions will be converted by the build process

/* to a definitions of SETUP_DATA fields.

/***********************************************************/

if ABOVE_4G_PCI_DECODE

UINT8 Above4gDecode; //[Disable]\ Enable

endif

If in one bios the setting is present, the code that "enables" 4G decoding sets EFI_PCI_HOST_BRIDGE_MEM64_DECODE in Allocation Attributes.

PciHostBridge

//This "FOR" loop will construcr HOST/ROOT bridge infrastructure and will

//try to map each root collected in call CreateRootBusData() to it's correcponded HOST

//using HbCspMapRootBrgToHost() CSP hook. For MULTY-HOST systems this hook must be ported

for(i=0;i<gRootBusDb.ItemCount; i++){

PCI_BUS_XLAT_HDR *roothdr=(PCI_BUS_XLAT_HDR*)gRootBusDb.Items[i];

PCI_BUS_XLAT_HDR *nexthdr=NULL;

ASLR_QWORD_ASD *busrd;

UINT64 aa=0, ra=0;

//---------------------------------------

//fill Allocation Atributes Property.

//Based on Token values of COMBINE_MEM_PMEM and ABOVE_4G_PCI_DECODE

if(COMBINE_MEM_PMEM) aa |= EFI_PCI_HOST_BRIDGE_COMBINE_MEM_PMEM;

if(ABOVE_4G_PCI_DECODE){

aa |= EFI_PCI_HOST_BRIDGE_MEM64_DECODE;

ra |= EFI_PCI_ATTRIBUTE_DUAL_ADDRESS_CYCLE;

}

It’s just an unused string

So, i asked AsRock to fix the above 4G decoding in my bios and they sent me an updated one. They also warned me:

“Please remind that this BIOS have modified the Intel RC code.

If your GPU-Z or device manager could not detect the graphic card, we suggest re-flashing this BIOS again to check if the symptom still exists.”

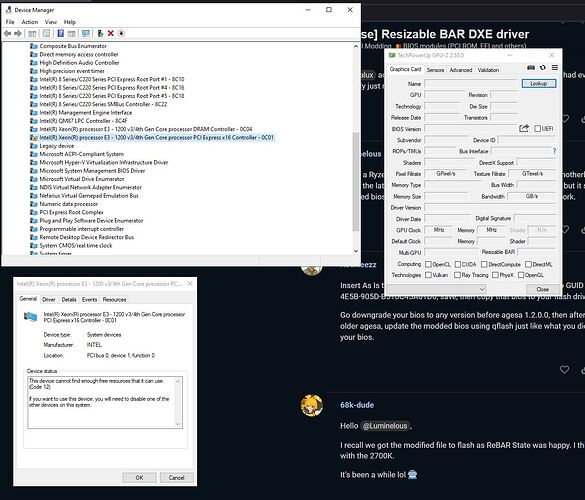

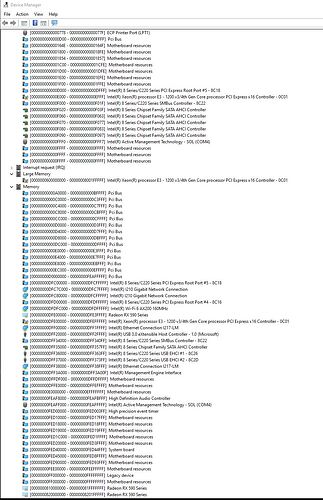

And just like the AsRock support warned me, i am getting Code 12 error for PCI-E controller in device manager and GPU is not recognized at all when above 4G decoding is enabled. Is it possible to make it work or should i ask AsRock for another try? Im adding the new modded bios: https://download.asrock.com/IPC_TSD/IMB1801.70H

you can fix this easily with DSDT edit yeah, the instructions are on GitHub wiki it mentions that most ASRock boards need it.

Try this and see if above 4g decoding works (make sure you could do full UEFI/Disabled CSM Boot first): IMB1801H-Mod.rar (4.8 MB)

if it works, try rebaruefi (run as admin) and set it at 13 (8GB).

I flashed your modded bios. The code 12 problem seemed to be gone, everything working fine (above 4G decoding reported as working by GPU-Z), then i set the rebaruefi to 13 (8gb) and rebooted, windows booted without a problem but GPU is not working again, getting code 12 for PCI-E controller and 45 for GPU

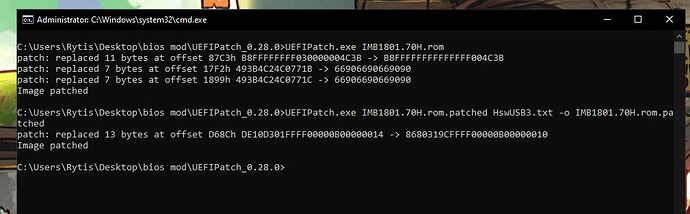

I patched the IMB1801.70H file that Asrock provided (old patches file I think)

4 patches applied

-

PciBus | Remove <16GB BAR size limit (Ivy Bridge/Haswell)

-

PciBus | Increase 256 byte configuration space limit to 4096 byte allowing access to PCIe extended configuration space

-

PciHostBridge | Remove 4GB limit for PciRootBridgeIo.Mem both

Yes, i think UEFIpatcher applied 4 patches for me as well but i used the bios modded by Koekieezz since i could not do the DSDT patching. CPU is Haswell mobile, i7-4900MQ

Edit: it seems to apply 2 patches + an additional one for USB 3

yes, that is exactly what i had, pcibus + host + usb only… seems asrock needs to examine the modded bios i provide and see the diff between the rev G and rev H diff.

i have a wonky idea

try to extract amiboardinfo and pcibus from the 1st rev G mod i gave, then make 3 diff bios based on Rev H mod i gave:

1 using modded AmiBoardInfo from 1st mod rev G

1 using modded PciBus from 1st mod rev G

1 using both modded AmiBoardInfo and PciBus from 1st mod Rev G.

see which one would work.

one thing to notice is that AmiBoardInfo size on rev G is smaller from stock vs rev H.

Maybe, try to extract AmiBoardInfo only from rev H i gave yesterday and replace it to Rev G.

Should i swap the whole AmiBoardInfo and PciBus section or only the PE32 body?

Edit: tried to swap only the PE32 body, flashing got stuck at crashless check at 0% and bios got bricked, had to flash back with CH314a

@karalux just use ASRock updated 4G decoding BIOS and DSDT fix.

Don’t use modules from old BIOS it won’t work they don’t support 4G decoding.

Do you mean DSDT fix only and no UEFIpatch patches?

@karalux Do both

i did both tho? the rev H i gave was dsdt patched…

May the problem be is that not all needed patches from the patches.txt file are being used?

@karalux It’s applying everything that it needs, there’s no issue there