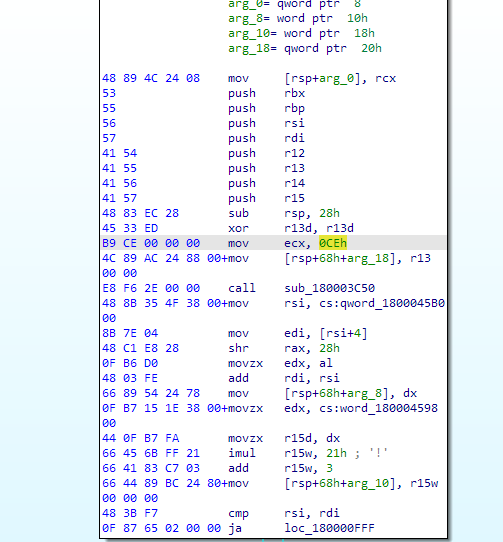

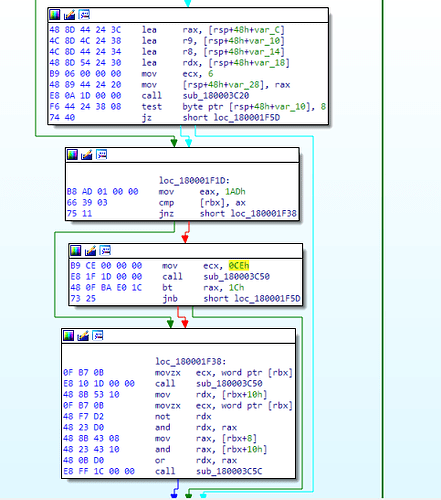

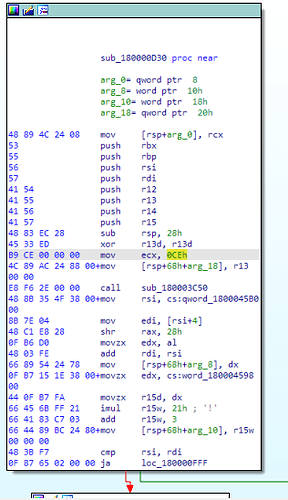

EDIT: enough guessing, here’s a peace of code with additions.

//MSR1(1) bit is set

//MSR1(0) bit is not set

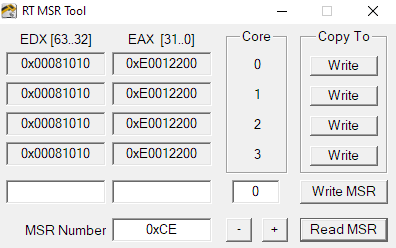

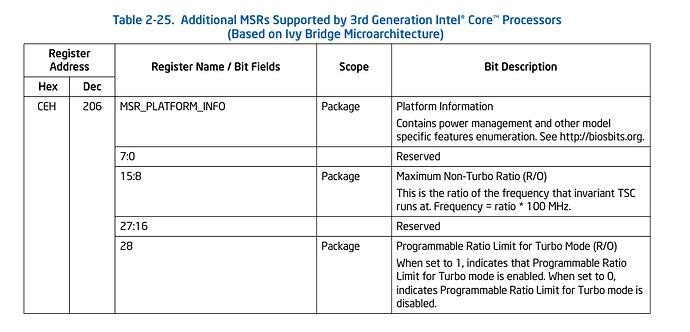

{0xce, MSRTYPE_RDONLY, MSR2(0,0), "MSR_PLATFORM_INFO", "", {

{ 63, 4, "NOT DOCUMENTED BITS (probably can allow MSR_OC_MAILBOX)", "R/O", PRESENT_DEC, {

{ BITVAL_EOT }

}},

// Skip 12 bits, proceed from the 60th.

{ 59, 12, RESERVED },

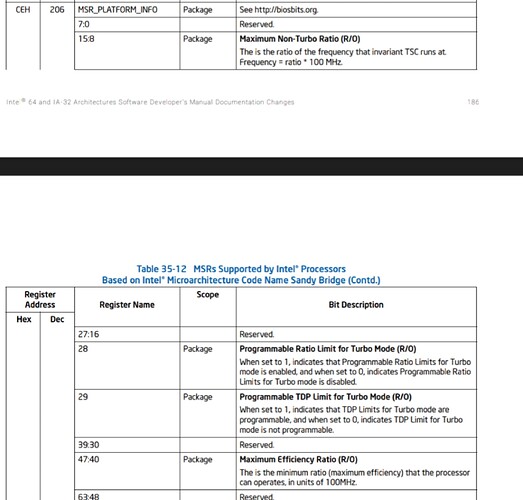

{ 47, 8, "Maximum Efficiency Ratio", "R/O", PRESENT_DEC, {

{ BITVAL_EOT }

}},

{ 39, 8, "Core Voltage", "R/O", PRESENT_DEC, {

// MSR_PERF_STATUS[37:32] * (float) 1/(2^13)

{ BITVAL_EOT }

}},

{ 31, 1, "Number of ConfigTDP Levels", "R/O", PRESENT_BIN, {

{ MSR1(0), "Additional TDP level(s) not available" },

{ MSR1(1), "Additional TDP level(s) available" },

{ BITVAL_EOT }

}},

{ 30, 1, "Low Power Mode Support/Programmable TJ Offset", "R/O", PRESENT_BIN, {

{ MSR1(0), "not supported" },

{ MSR1(1), "supported" },

{ BITVAL_EOT }

}},

{ 29, 1, "Programmable TDC-TDP Limit for Turbo Mode", "R/O", PRESENT_BIN, {

{ MSR1(0), "TDC and TDP Limits for Turbo Mode are not programmable" },

{ MSR1(1), "TDC and TDP Limits for Turbo Mode are programmable" },

{ BITVAL_EOT }

}},

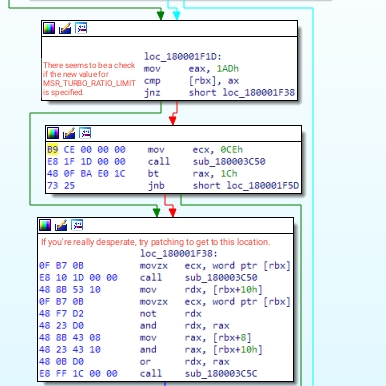

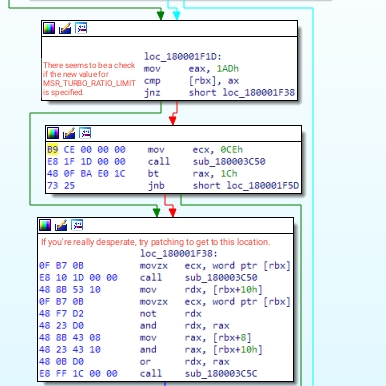

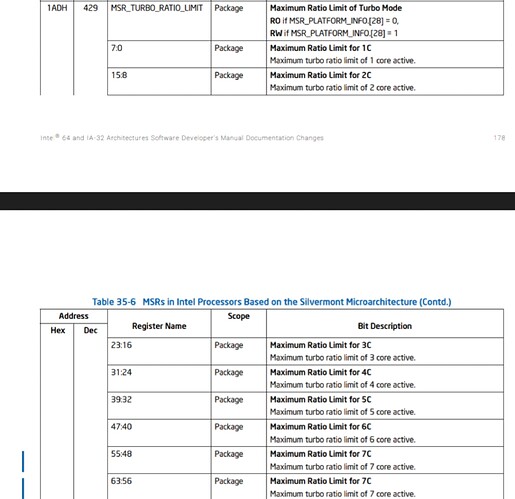

{ 28, 1, "Programmable Ratio Limit for Turbo Mode of MSR_TURBO_RATIO_LIMIT 0X1AD", "R/O", PRESENT_BIN, {

{ MSR1(0), "Programmable Ratio Limit for Turbo Mode is R/O" },

{ BITVAL_EOT }

}},

// Skip 5 bits, proceed from the 27th.

{ 27, 5, RESERVED },

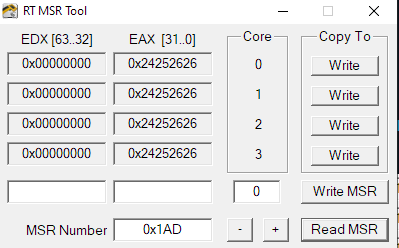

{ 23, 1, "Programmable Ratio Limit for Turbo Mode of MSR_TURBO_RATIO_LIMIT 0X1AD", "R/O", PRESENT_BIN, {

{ MSR1(1), "Programmable Ratio Limit for Turbo Mode is R/W" },

{ BITVAL_EOT }

// Skip 8 bits, proceed from the 23rd.

{ 22, 7, RESERVED },

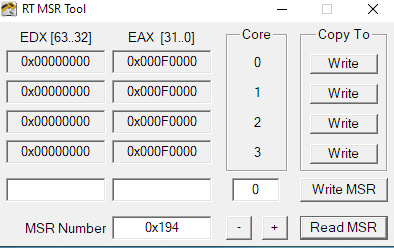

{ 15, 8, "Maximum Non-Turbo Ratio", "R/O", PRESENT_DEC, {

/* This is ratio of the frequency that invariant TSC runs at. The invariant

* TSC requency can be computed by multipying this ratio by 133.33 Mhz.

*/

{ BITVAL_EOT }

}},

// Skip 7 bits.

{ 7, 7, RESERVED },

{ 0, 0, "NOT DOCUMENTED BIT", "R/O", PRESENT_BIN, {

{ BITVAL_EOT }

}},