I used uefitool but I got another file ending and not .raw like you did. But it was no problem, I used your attached modules from zip file and compiled them. I even changed the one bit from F0 to F4 using hex editor for syncing all cores.

So everything is fine. Thank you very much for this guide. How did you figure out the difference between 4 and 6/8 core in pei module and acpi table? did you read all the intel related documents or did you compare z370 bios with z170 ones?

@oldirdey

Hi, sorry for bothering you. Could you suggest to me a valid disassembler like the one in your attached image on your previous post please ?

@Sylar76 Hey, no problem asking about it. You will laugh, but I used an online disassembler for comparing. https://defuse.ca/online-x86-assembler.htm

@dsanke

About uncore ratios. It looks like it is expected for cache ratio to have offset -3 from core ratio. If I set cache max ratio at 48, core at 48 I only get cache ratio of 45. If I set core at 45 I get cache 42. I must set higher cache min ratio to come closer to core ratio - if cache min ratio is set to 47, core to 48 then I get cache ratio of 47 all time (won’t downclock).

@Sylar76 - Hopper is OK free disassembler, and then there is IDA but it costs unless you know where to look.

The guide was meant for advanced users. If you don’t know how to use a disassembler, there is no need for using it. It looks like the code is similar among vendors (ASUS, MSI, GIGABYTE) - the step 1 can be automated. I updated step 1 with info. Follow the steps on your risk - make sure you know (and there is a way) how to recover when something goes wrong (flashing not working BIOS).

@s.napi

I use rw-everything to check msr 0x620h .

The cache ratio can only reach 28x (0x1c) .

Even though I set it to 0x1f or higher , it still got 28x .

But when I set it to 0x1b or lower , it works.

I have the same observations - I can set lower but not higher (than what is set in BIOS setup) ratios in Windows (via writing to MSR). Neither for cache nor for core. The Intel XTU utility can set higher core ratios but not cache. Try setting cache min ratio in BIOS setup, if you have this option. The Z370 BIOSes have the option for locking cache ratio to core ratio, I think.

@s.napi

When I use Z370 port BIOS , the cache ratio default set to max all core turbo . For my QN8J is 31x .

The Z370 BIOS doesn’t have more option than B150 BIOS , it just let these options work.

@s.napi I tried to change Core and Cache Ratio with XTU to higher values then set in bios. It works without problem. Changed Core from 47 to 48 and cache from 44 to 45. But I am using Win 7, maybe there is a difference to Win 8.

Do I only have to flash the bios you posted above to get a working 8700k on M8I?

@aleban new link here: https://files.fm/u/cuwejfv3

Flash this by Spi programmer and then S.napi bios via flashback.

@aleban if you did everything right as mothaj explained, you should end with this. Take note of ME Version 0.0.0.0. If you can still read the Version Number something went wrong and you don´t need to try coffee lake cpu.

Thank you all!

Tonight then I try with the update as explained in the second post here ([GUIDE] Coffee Lake CPUs on Skylake and Kaby Lake motherboards ).

At that point I see if Intel ME is correct.

Hoping not to destroy something.

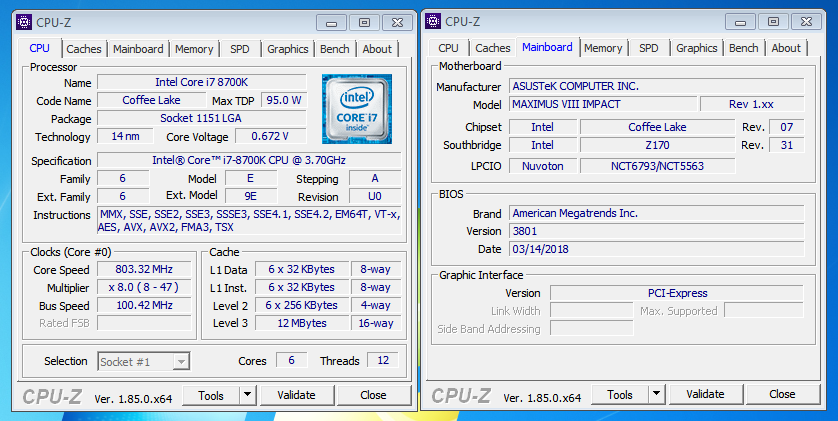

@oldirdey I see that your cpuz shows the graphic interface as pci-express only as well. I wonder why this is. I remember comparing the xml files pre/post z370 sku change a while back and don’t recall anything extraordinary. Seems to be purely cosmetic though.

@aleban

Make sure you save your original BIOS file (read image using SPI) so you don’t loose your board specific information (serial number, MAC address). Use FD44Editor to copy this information to new BIOS before flashing via SPI.

And if I haven’t SPI programmer? ![]()

@s.napi

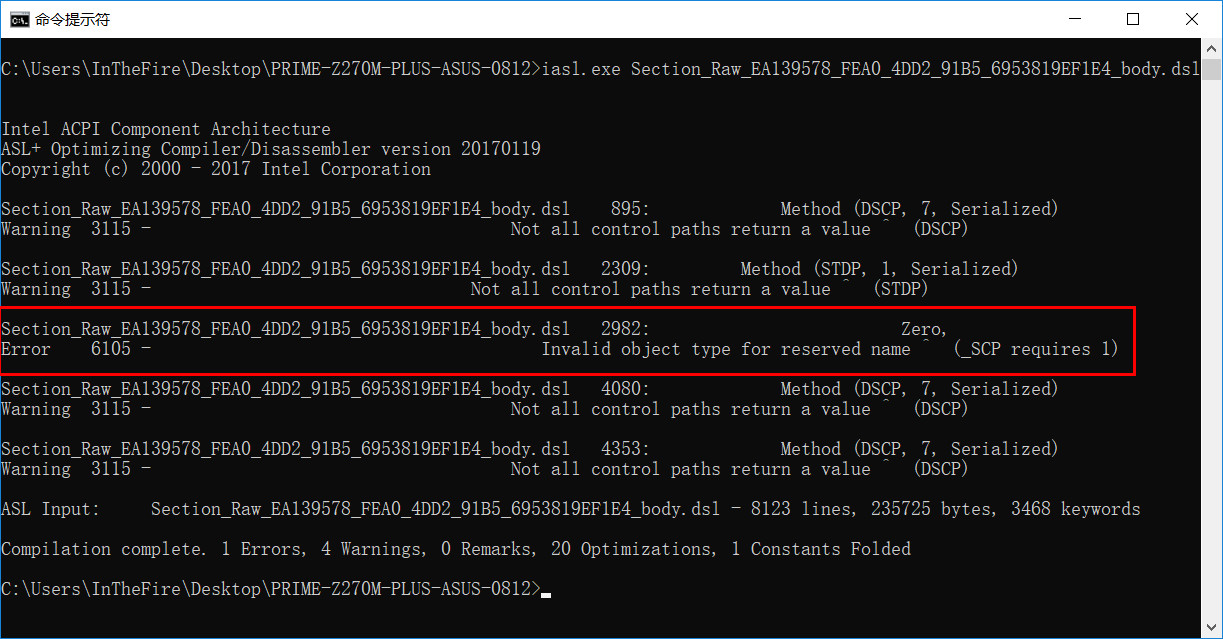

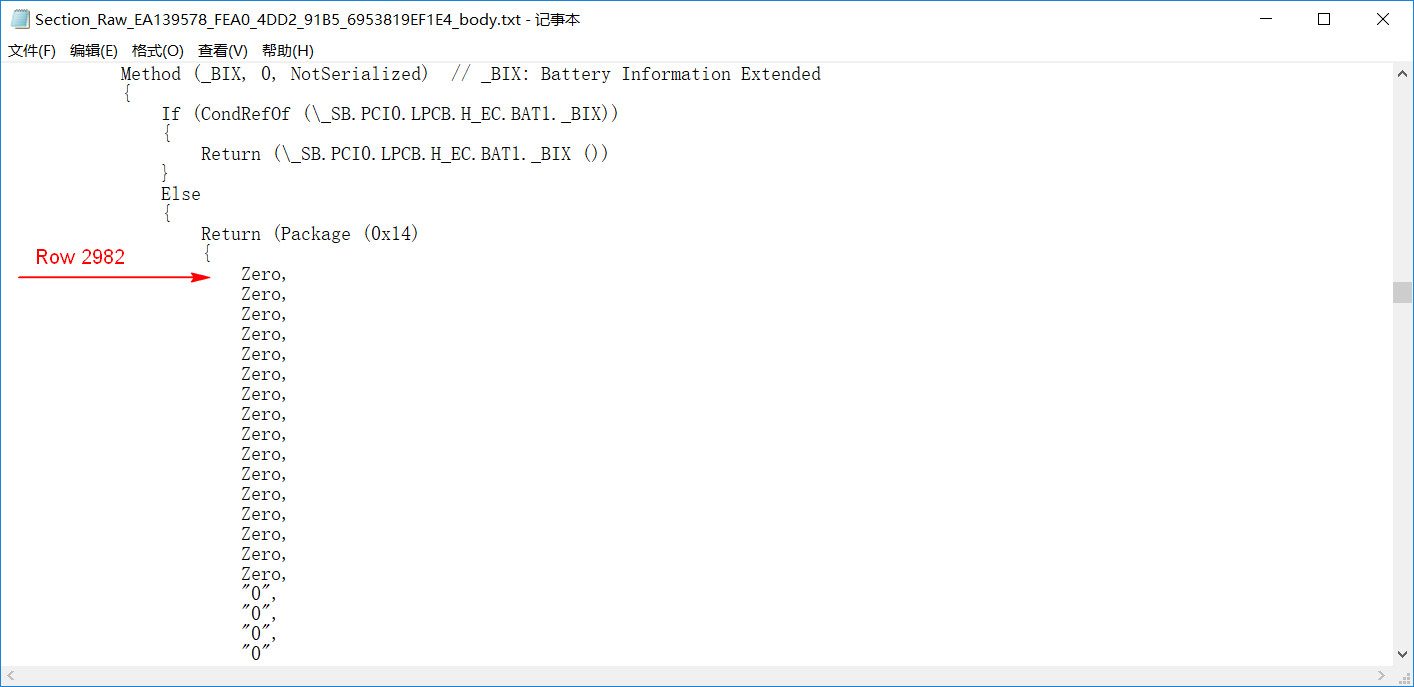

Hi, I met a problem during the process…there’s 2 section-dsl files(out of all)I could’t compile with iasl tool…even I changed nothing of the dsl file…

And I changed different revisons of the tool for that, still couldn’t work.

Can you help me check how the error comes?

Section_Raw_EA139578_FEA0_4DD2_91B5_6953819EF1E4_body.txt (230 KB)

Section_Raw_3BBB09DA_1E0F_469B_8997_D440F101D6F1_body.txt (346 KB)