intel_mc.zip (3.2 MB)

None of these items are new. In other words, they are only new in relation to the last official database (r270). In fact, the 806F3 version is already included in r270. And the other five I posted five days ago. Use the one I keep updating. Which, by the way, is not a challenge at all. ![]()

MCE.rar (73.8 KB)

A post was merged into an existing topic: MC Extractor: Intel, AMD, VIA & Freescale Microcode Extraction Tool Discussion

Genoa

cpu00A10F11_ver0A10113E_2023-06-20_4840C55C

cpu00A10F12_ver0A10123E_2023-06-20_4EE5C2BB

Bergamo

cpu00AA0F01_ver0AA00116_2023-06-19_BCD5C29B

cpu00AA0F02_ver0AA00212_2023-06-19_6C81D673

…and updated MCE.db

AMD.rar (94.8 KB)

Whiskey Lake-U

cpu806EB_platD0_ver000000F4_2023-02-23_PRD_B065A585

Comet Lake-U

cpu806EC_plat94_ver000000F8_2023-02-26_PRD_1A38BF55

Sapphire Rapids

cpu806F4_plat87_ver2A0000A0_2022-07-12_PRD_9F69A556 (old)

cpu806F5_plat87_ver2A0000A0_2022-07-12_PRD_9F69A555 (old)

cpu806F6_plat87_ver2A0000A0_2022-07-12_PRD_9F69A554 (old)

cpu806F7_plat87_ver2A0000A0_2022-07-12_PRD_9F69A553 (old)

Comet Lake-H

cpuA0652_plat20_ver000000F8_2023-02-23_PRD_BFD991E9

Comet Lake-U

cpuA0660_plat80_ver000000F8_2023-02-23_PRD_B034DA71

…and updated MCE.db

Intel.rar (937.2 KB)

@ Istvan, here: https://www.intel.com/content/www/us/en/developer/topic-technology/software-security-guidance/processors-affected-consolidated-product-cpu-model.html but a little obsolete!

IceLake-SP

cpu606A6_plat87_ver0D0003A5_2023-03-30_PRD_9B6921E3

…and updated MCE.db

Intel.rar (365.8 KB)

Tiger Lake-H

cpu806D1_platC2_ver00000046_2023-02-27_PRD_08E6188A

Alder Lake-S

cpu90672_plat07_ver0000002E_2023-04-18_PRD_5A2EB635

cpu90675_plat07_ver0000002E_2023-04-18_PRD_5A2EB632

Kaby Lake-G/H/S/X

cpu906E9_plat2A_ver000000F4_2023-02-23_PRD_053E83C6

Raptor Lake-H/P/PX/U

cpuB06A2_platE0_ver00004119_2023-06-06_PRD_705FCD38

Raptor Lake-P

cpuB06A3_platE0_ver00004119_2023-06-06_PRD_705FCD37

Raptor Lake-HX/S

cpuB06F2_plat07_ver0000002E_2023-04-18_PRD_5A2CB5B5

cpuB06F5_plat07_ver0000002E_2023-04-18_PRD_5A2CB5B2

Updated MCE.db (v1.90.2 r274 Dev, 08/04/2023)

Intel.rar (709.9 KB)

Raptor Lake-H/P/PX/U

cpuB06A2_platC0_ver00004114_2023-03-15_PRD_EC22FEF6

cpuB06A3_platC0_ver00004114_2023-03-15_PRD_EC22FEF5

Updated MCE.db (v1.90.2 r274 Dev, 08/07/2023)

Intel_20230807.rar (285.1 KB)

!New_cpu806F1_plat10_ver80000350_2021-10-23_PRE_C8F0D614

!New_cpu806F2_plat87_ver8C0004E0_2021-11-12_PRE_DD2312C1

!New_cpu806F3_plat87_ver8D000390_2021-11-12_PRE_28635F3A

cpu806F1_plat10 = SPR-HBM A0 (xeon max)

Intel.zip (1.5 MB)

cpu50653_plat97_ver01000181_2023-03-23_PRD_039BF880

cpu5065B_platBF_ver07002703_2023-03-21_PRD_609283DB

cpu806C2_platC2_ver0000002C_2023-02-27_PRD_B67C5F64

cpu806F4_plat10_ver2C000271_2023-05-15_PRD_51465829

cpu806F5_plat10_ver2C000271_2023-05-15_PRD_51465828

cpu806F6_plat10_ver2C000271_2023-05-15_PRD_51465827

cpu806F8_plat10_ver2C000271_2023-05-15_PRD_51465825

cpuA0661_plat80_ver000000F8_2023-02-23_PRD_C3B0851C

cpuB06E0_plat11_ver00000011_2023-04-12_PRD_CC845E75

Updated MCE.db (v1.90.2 r274 Dev, 08/08/2023)

Intel_20230808.rar (1.0 MB)

Raptor Lake-HX/S

cpuB0671_plat32_ver0000011C_2023-08-17_PRD_C4C16248

Updated MCE.db (v1.90.2 r275 Dev, 08/31/2023)

Intel_230831.rar (281.1 KB)

Raptor Lake-HX/S

cpuB0671_plat32_ver0000011A_2023-07-16_PRD_7E47D5BF (old)

Updated MCE.db (v1.90.2 r275 Dev, 09/02/2023)

Intel.rar (281.2 KB)

cpuC06F2_plat87_ver210000E0_2023-06-16_PRD_70EB34A2

cpuC06F1_plat87_ver210000E0_2023-06-16_PRD_70EB34A3

Intel.zip (1.0 MB)

HP Desktop Workstation U60 Family

(As requested).

Thanks! In order to be sure, are there the official/stock/raw files? Is the source public? So that I know if I must set the size to 0x16C0. The other Ax series microcodes have 0x15C0 size.

Maybe my mistake. It should be 0x17C0

It is from a Lenovo Bios. It can be found here:

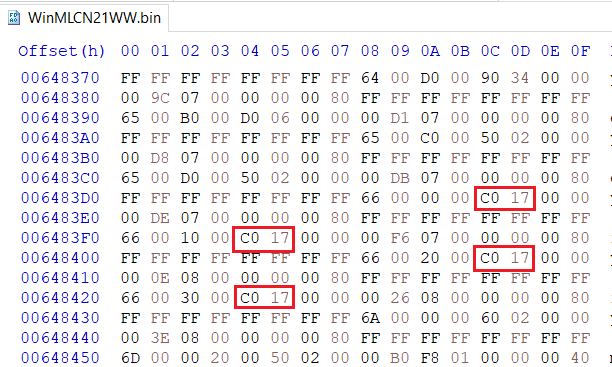

It is definitely not 0x17C0 as that would cross over padding and other data.

I checked out some Asus laptops with those Phoenix CPUs and a maximum of 0x1700 can be observed superficially. However, that is clearly alignment padding for 0x16C0.

Inspecting the area before the microcode, it appears that it is an AMD PSP module ($PS1). Now, I’m not familiar with AMD PSP but some quick reverse engineering later, I can see the following:

The $PS1 header is 0x100 sized. At offset 0x4 (and 0x50, probably only when uncompressed ? - doesn’t matter much), we have the actual payload size. In this case: 0x15C0. At offset 0x6C, we have the full PSP module size. In this case: 0x17C0.

It’s clear that the header is 0x100, the payload is 0x15C0 (what we need for MCE) and thus, the last 0x100 bytes must be an RSA 2048-bit signature. So the format, as reversed:

0x100 → $PS1 Header

0x15C0 → Microcode Blob

0x100 → RSA Signature

0x17C0 → Total

The size of 0x15C0 also matches with all other Ax-series CPUIDs and is referenced at the microcode header at offset 0xA-0xC, which used to be reserved before AM5, but it seems to contain the microcode size, once multiplied by 0x10 (0x015C x 0x10 = 0x15C0).